### WP 2.4 Interface electronics

Peter Göttlicher, DESY-FEB, September 16th , 2009

- module concept

- technical challenges

- mechanical dimensions

- fully open: specifications for the ASIC's

--- slow/fast control in quadrant see tomorrow

### Module concept

## Technical challenges

See talk from Igor Sheviakov

- ADC's : 50MS/s, >10 bits above noise OK. - High data transfer 700Mbits/s through connections OK. - Access to memory for 50MS/s and 10GbE, concept last meeting OK. - Own test board with 10GbE OK. **OK**?? -Connector densities see next slides: concept Discussed today with ASIC ONLY, if ASIC: gain-bits on analogue lines needs two analogue boards, gives also more compact detector head.

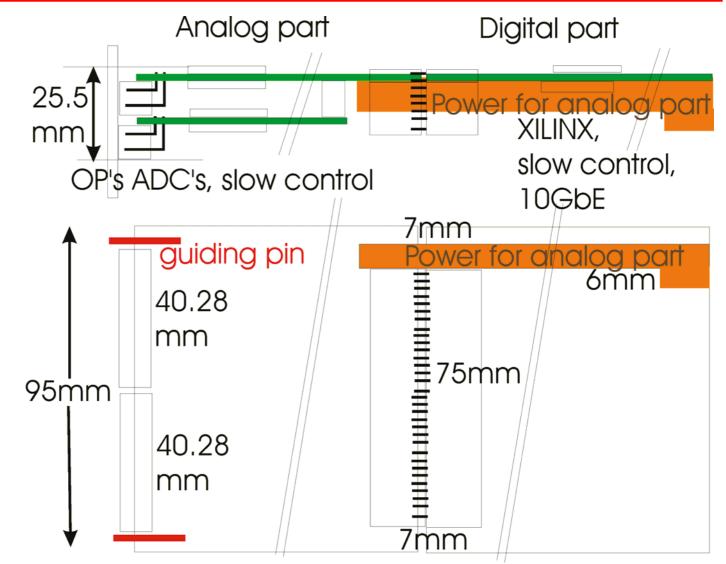

# Mechanical dimensions: width to be fixed

#### Module width of 95mm would allow

- For 2mm of rails each side, 91 mm for components.

- If needed, forced air stream, one side in, other out.

- Some freedom for for mechanical design

- Some shifts of electronics against sensors: More distance to beam.

# Connections to quadrant-backplane

Signal count

- 200 64 analog from ASIC in pattern GND-sig-sig-GND

- 3 Fast clocks from quadrant in GND-sig-sig-GND

- system-clk(<~100MHz)

- convert-clk(50MHz), bunch-clk

- coded length for train-start/end

for convert-start/-end/pixel-incr.

Slow control:

module/extension/mode micro-controller

slow control for analog part (I<sup>2</sup>C) from μC

slow control for digital part (I<sup>2</sup>C-like) from FPGA

Reserve for remote firmware management

222 pins: Fits to 4x SAMTEC TML-132-02-S-D-RA-10 = 256

9

# Connections from analog to digital

Signal counts as pairs ("/2" = single line of pair)

- 80 from ADC's: 700Mbits/s

- 3 Fast clocks from quadrant

- system-clk(<~100MHz)

- convert-clk, bunch-clk

- coded length for train-start/end for convert\_start/end/pixel-incr.

- 2 power for digital driver

- ADC-clock from digital to analog

September 16<sup>th</sup>,2009 Slow control:

- 1/2module select (FPGA-Q)

- ADC-chip-select from FPGA to analog part

- ADC slow control+power-down

- slow control for digital part (I<sup>2</sup>C like) from FPGA-Q

- slow control for digital part (I<sup>2</sup>C like) from  $\mu$ C

- reserve for remote firmware management

$\begin{array}{r} \text{Peter Göttlicher, DESY-FEB, is} \\ \text{S/C} \\ \text{S/C$ Fits to 3x ERNI: ERmet ZD (female 973032, male 973101) = 120 pairs:

Specification coming from ASIC

Discussions ongoing today and tomorrow

If not settled, the concurrent engineering will fail! But: That is basics of time schedule!

Risk of developing wrong boards! too high or too low complexity!

Examples: Gain bits on analog: strongly defines the whole concept of mechanics and electronics Speed of analog and gain-bits: defines circuits and space

### Slow control :

Not covered today:

- slow control, is in close contact with central Work packages.

- It will tell also AGIPD control inside detector head in talk about WP2.5: control system