# General Status of the HPAD detector project

- Feedback from the XDAC

- Current situation

# General comments on projects

We felt that all of the projects currently have inadequate content regarding thermal issues. We encourage them all to devote some effort into thermal analysis as soon as possible. It is much easier to implement a cooling scheme early in a project than to have to retro-fit additional cooling near the end.

# General comments on projects

A similar comment should be made for calibration schemes. If on-line calibration will be needed, it needs to be thought about now. It could be that the calibration scheme should be a separate common work package, since all systems may need it.

# General comments on projects

We noticed a significant convergence of designs between the existing projects and the new proposal. They should look for shared content to provide economies of effort. One way, suggested by one of the speakers, would be to hold an ASIC "designer fest", at which details of proposed ASIC designs could be shared.

### General comments on projects

The efforts to develop detector simulations and provide samples of experimental or simulated data are potentially very useful, again for all the detector projects and for others. Software which enables 'end-to-end' beam line modeling is severely lacking in the synchrotron community, in contrast to the situation in the HEP community. This could be another joint effort separated out and drawing from wider resources.

### Specific comments on HPAD

We found that, in contrast to the LPD project, the schedule here was very conservative, in particular for the ASIC development. We felt that larger pieces of the design should have been included in the first submission. In general, the team needs to focus more tightly on a reduced parameter space if they are to converge to a working design in the time available. Many decisions were deferred to 2010, which is dangerously close to the starting date. For example, the pixel size should be fixed already, and in fact we had the impression that it was now fixed at 200um. This decision could well reduce some of the uncertainty in other aspects of the project

# Specific comments on HPAD

As mentioned earlier, their attempts to generate simulations of the detector response to realistic data are valuable to all, and this sub-project maybe belongs in WP-75, rather than localized here.

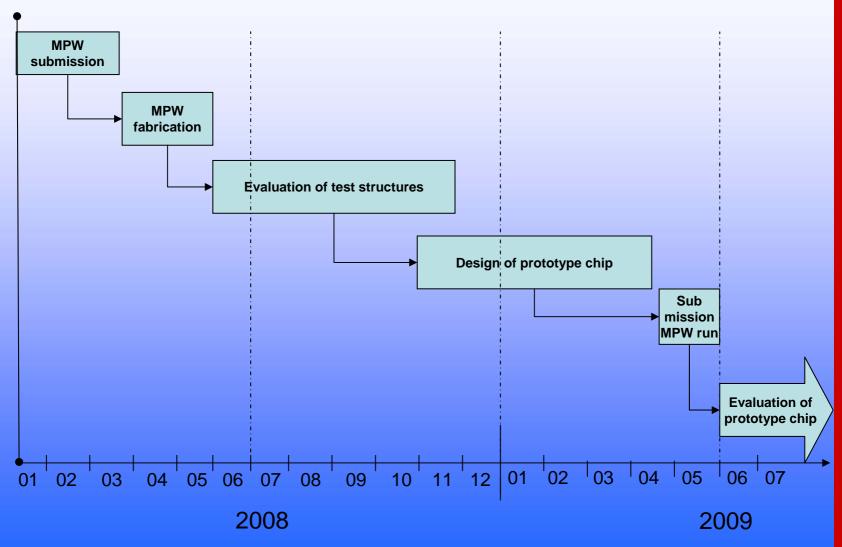

# Strategy for the development

- Design test structures in 0.13  $\mu m$  CMOS to test technology limits (MPW)

- Extensively Test these structures

- Design test chip; 16 x 16 pixels with different flavors

- Extensively test test chip.

- In parallel simulate detector performance and analyze science requirements

- Decide together with application scientists on exact pixel content → Phase II

# Personnel situation

### **Coordination:**

- Heinz Graafsma 40%

- Stefanie Jack 50%

### **Sensors:**

- Robert Klanner

- Johanna Pintilie (visiting scientist) 20%

- Matthias Schroeder (PhD) 100%

- Ajay Kumar Srivastava (PostDoc) 100%

- Georg Steinbrück (PostDoc)

- Hanno Perrey (Phd Student)

- J. Becker (PhD Student)

### **Detector and science simulations:**

Guillaume Potdevin (PostDoc) 100%

# Personnel situation

### **ASIC:**

- Ulrich Trunk (ASIC designer) 100% since November 2007

- Riccardo Mazzocco (ASIC designer, PhD) 100% since February 2008

- Hans Krueger (ASIC designer) 10%

- Bernd Schmitt (ASIC designer) 20%

- PostDoc at PSI under recruitment 100%

- Engineering support Bonn 30%

### **Interface and control electronics:**

- Peter Goettlicher 20%

- Manfred Zimmer 10% (Engineer)

- Igor Cheviakov 60% (Engineer)

- Petr Vetrov 10% (Engineer)

- Hans Wentzlaff 20% (Engineer)

### **Control electronics:**

Moved to separate WorkPackage

### **Interconnect and mechanics:**

- Beat Henrich 10%

- Helmut Hirsemann 20%

## Development of ASIC Design