## Vertically Integrated Circuits: Example of an Application to an x-ray Detector

Alessandro Marras

on behalf of the AGIPD collaboration

# Outline

- The goal and the obstacles to overcome

- X-ray sensors for advanced FEL

- Adaptive Gain Integrating Pixel Detector (AGIPD)

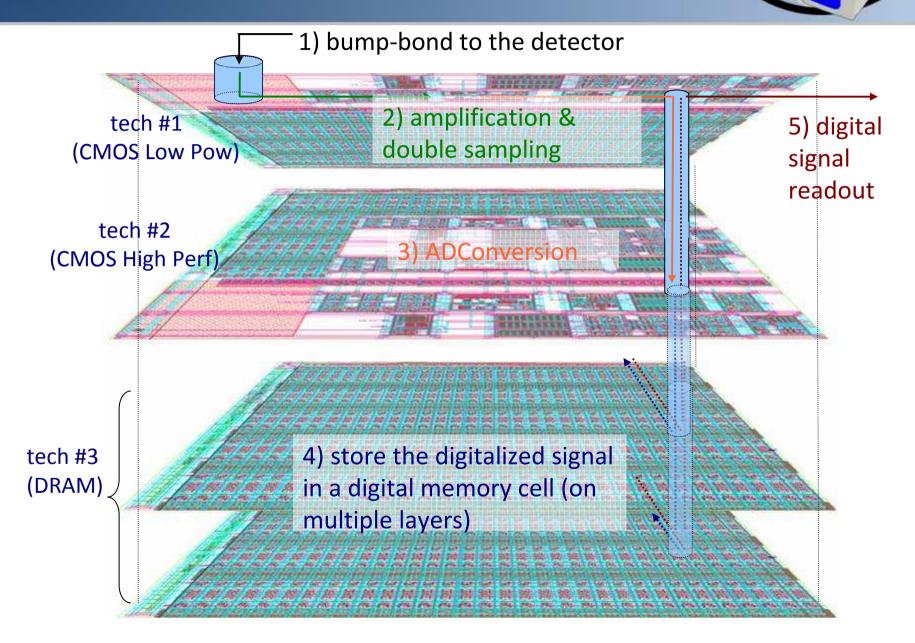

- 3DIC: a possible path to the solution

- design and test of 2-tier detector prototype

- TSVs & tier-to-tier contacts

- vertically integrated test circuits, matrix prototype

- Conclusion

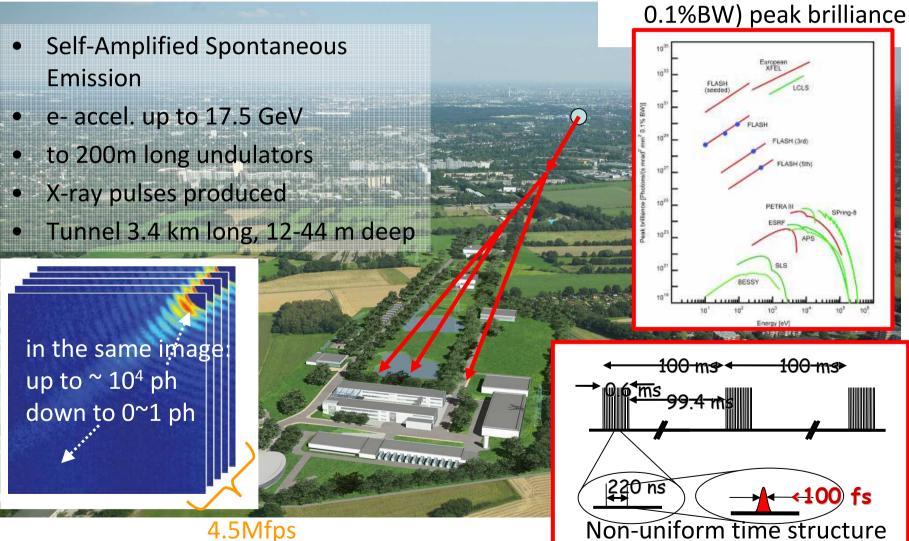

# The Motivation

$10^{33}$  ph/(s mm<sup>2</sup> mrad<sup>2</sup>

4.5Mfps

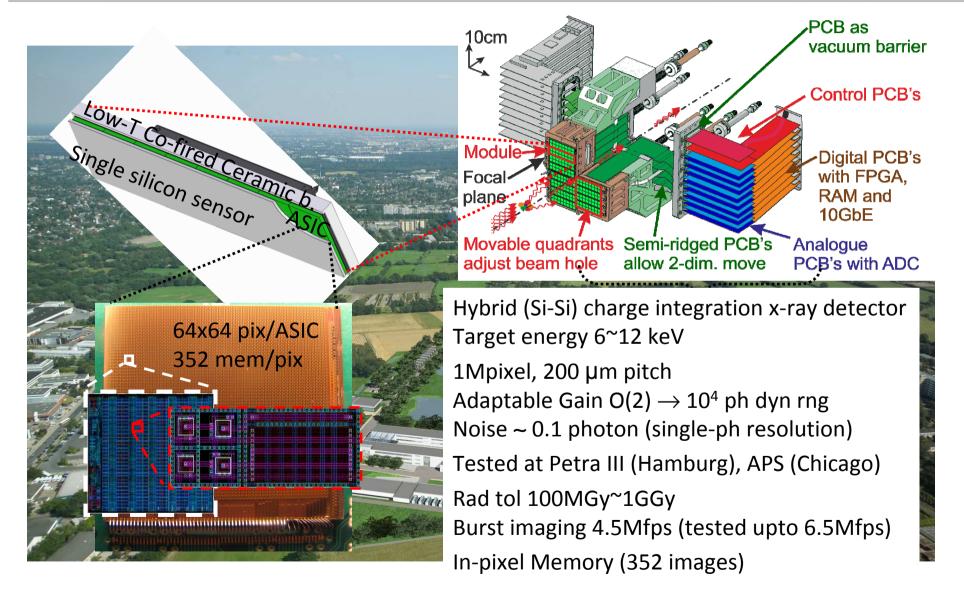

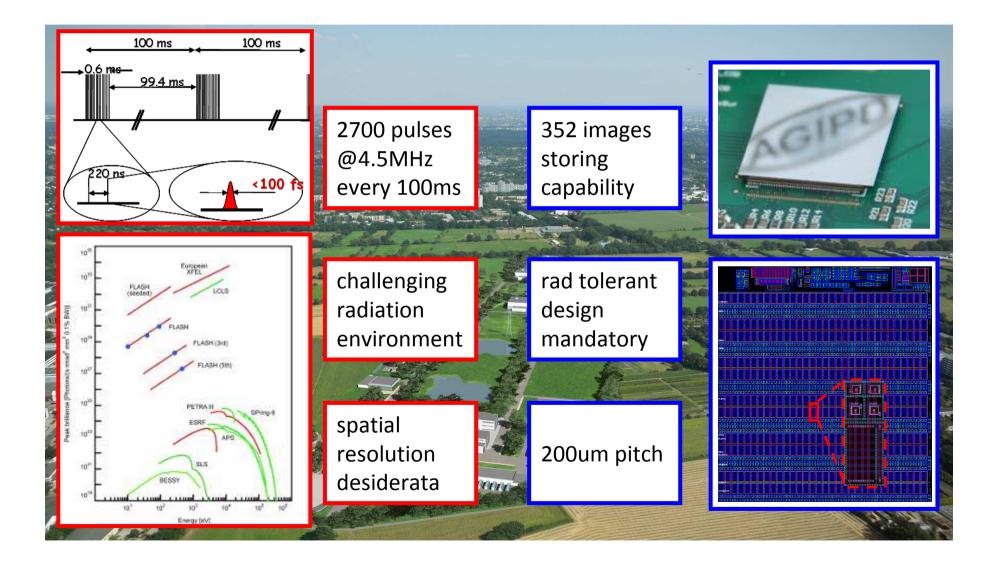

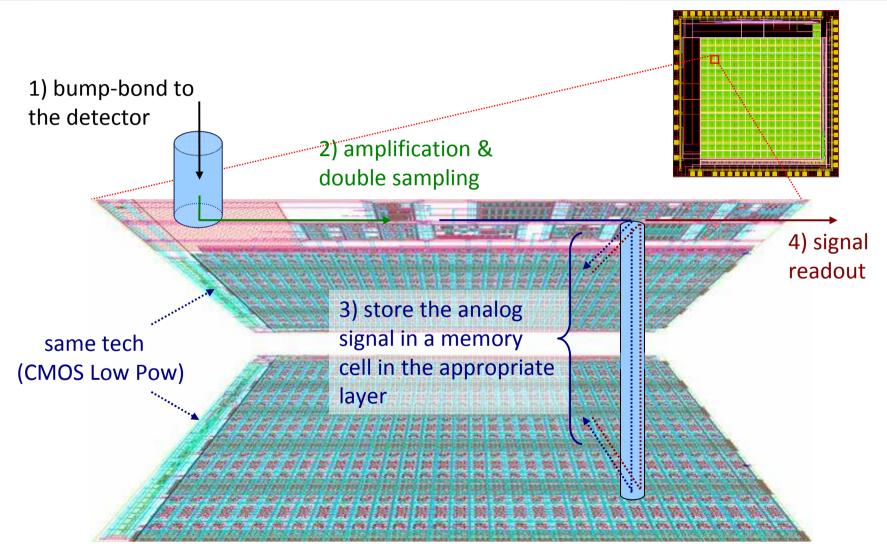

# A.G.I.P.D. (2D)

## but still...

## A possible solution (long term goal)

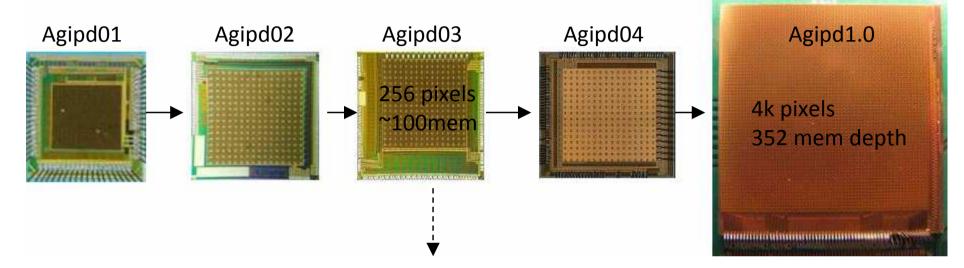

# The first step

# A path toward the solution

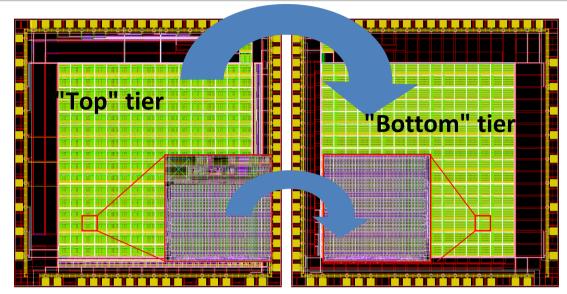

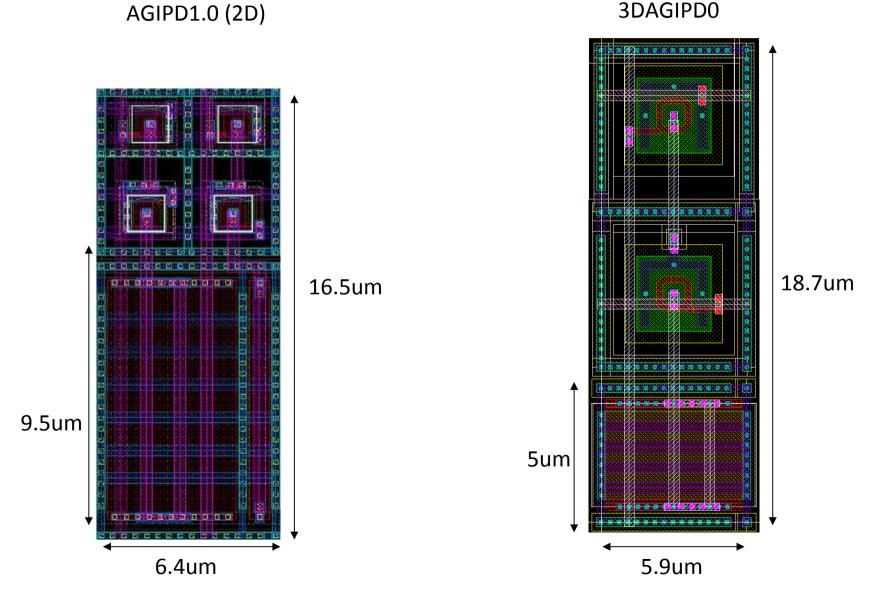

GF 130nm CMOS Low Power ARM SC library Tezzaron FaStack double-tier

T13C11 MPWrun, via CMP submitted 2011 delivered Jan 2014

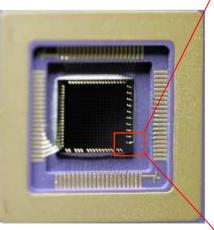

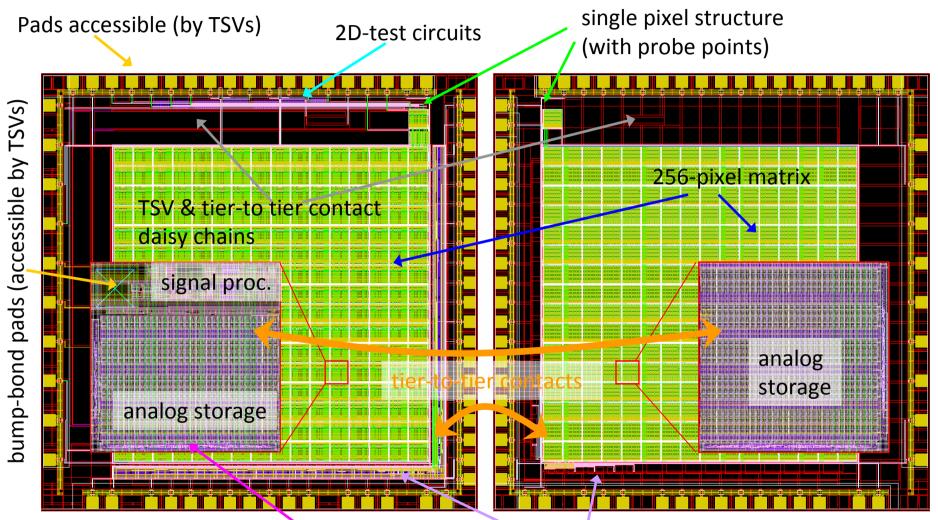

3D-AGIPD0

test structures + 256 pixels matrix 200um pitch 544 mem depth

simplified architecture: fixed gain (but reserving the space for multiple-gain circuits; equivalent memcell area)

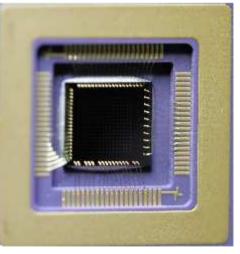

# The process at a glance

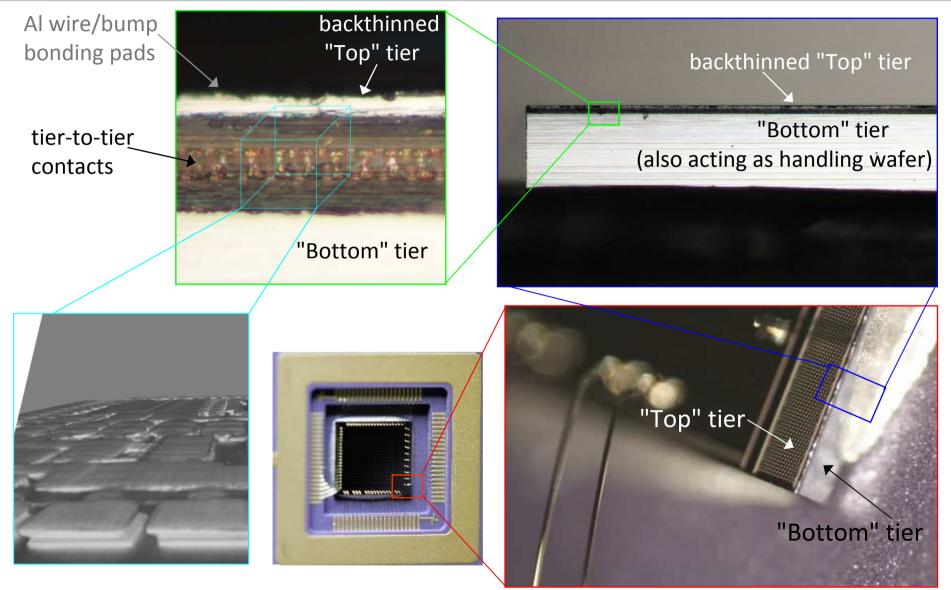

- 2x planar chip manufacture

- via-middle TSVs

- stacking and face-toface coupling

- back-grinding of the top tier and exposition of the TSVs

- Pad definition

## The process at a glance

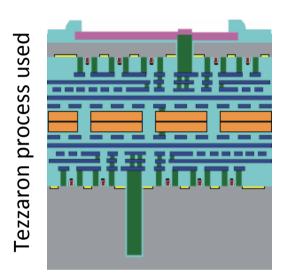

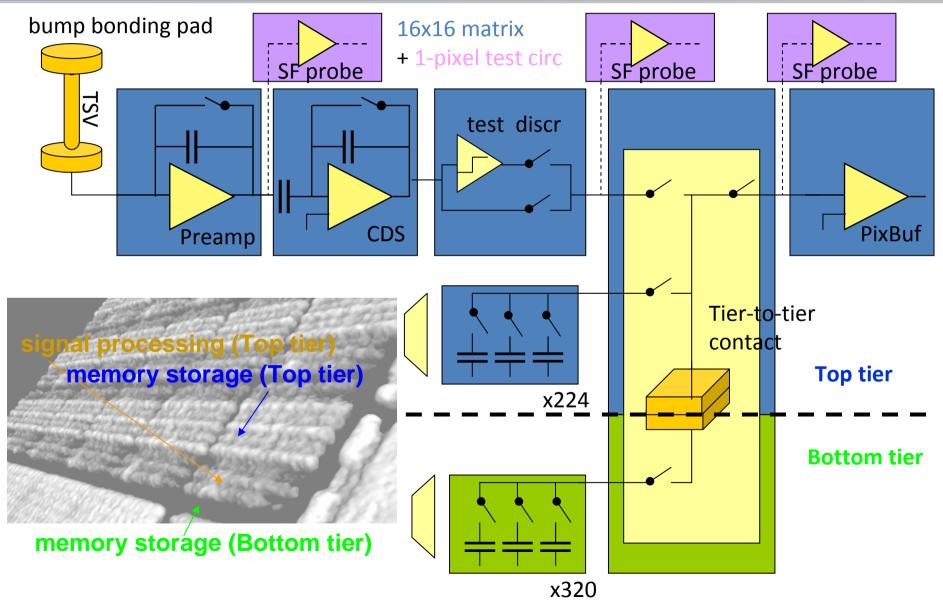

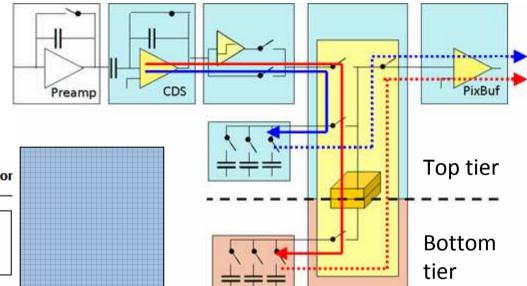

# pixel architecture

## chip architecture

SC-based addressing circuit (distributed on both tiers) both at the pixel level and at the array level

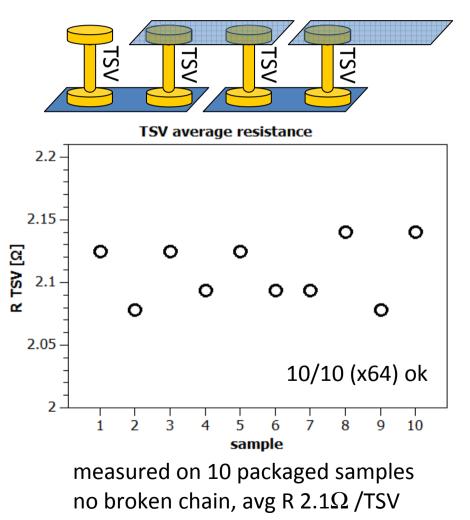

# **TSV contacts evaluation**

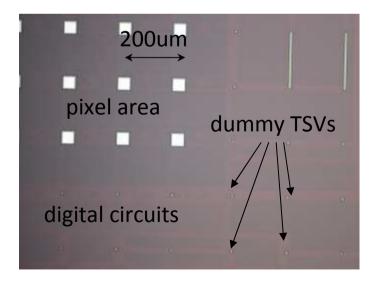

"via middle" TSVs Ø 1.2 um , landing on M1

locally: TSV-to-TSV distance down to ~4um however, globally: "uniform" density of TSVs recommended ( $\rightarrow$  uniform resistance to grinding)

$\rightarrow$  designer constraint: dummy TSVs

10x test structure for TSV evaluation: daisy chain of 64 TSVs, by connected M1/backM.

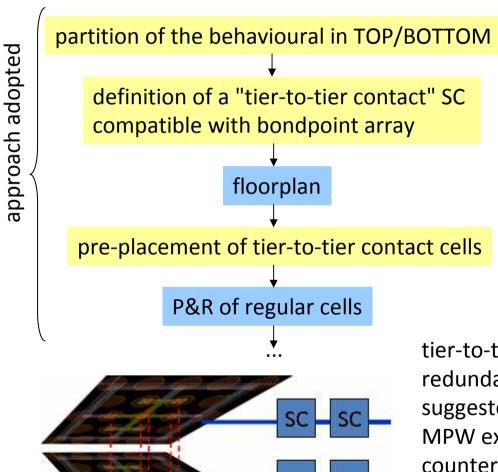

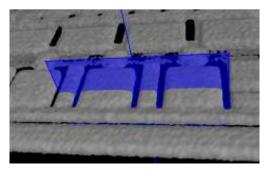

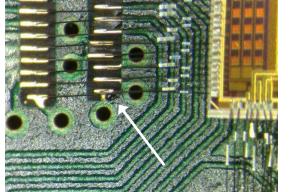

## Tier-to-tier contacts

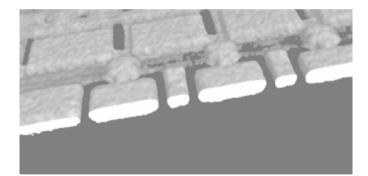

Cu-bondpoints (M6) used for tier-to-tier connectivity

tier-to-tier contact redundancy was suggested by 2009 MPW experience, to counter eventual tier misalignment

however ...

M<sup>3</sup>APS (courtesy of INFN-Perugia) submitted end 2009 Tomography by F. Beckmann (DESY)

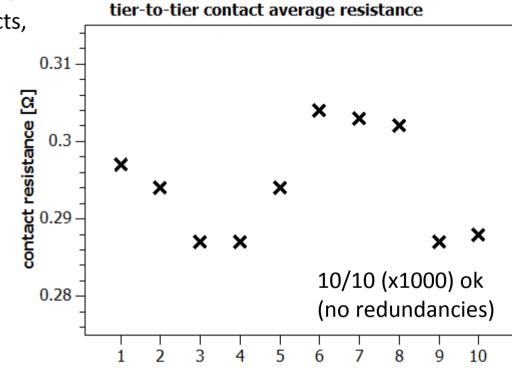

#### Tier-to-tier contact evaluation

10x test structure for contact evaluation: daisy chain of 1000 tier-to-tier contacts, connected in series using M5.

measured independently on 10 packaged samples no broken chain

x-ray tomography (F. Beckmann, DESY) also suggest better alignment

sample

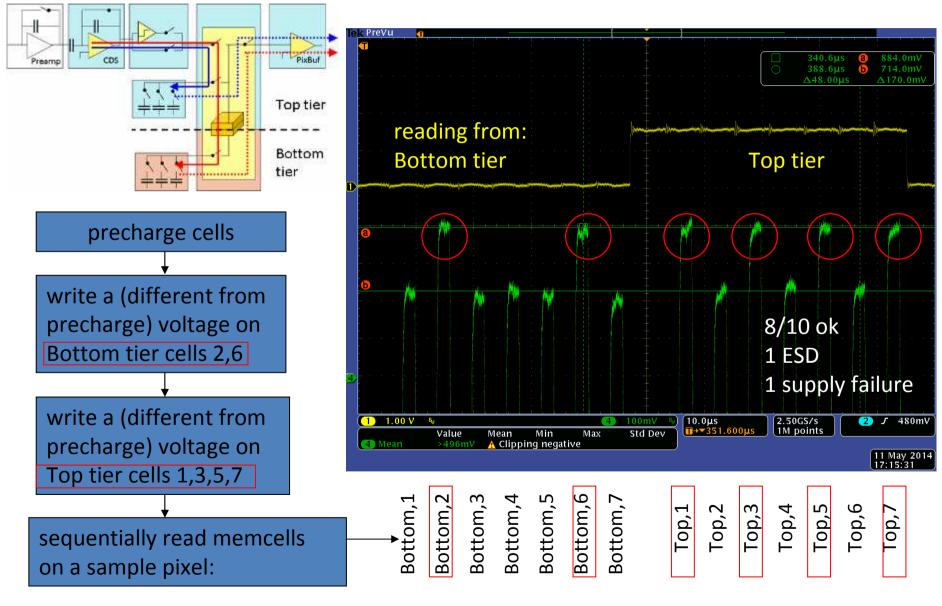

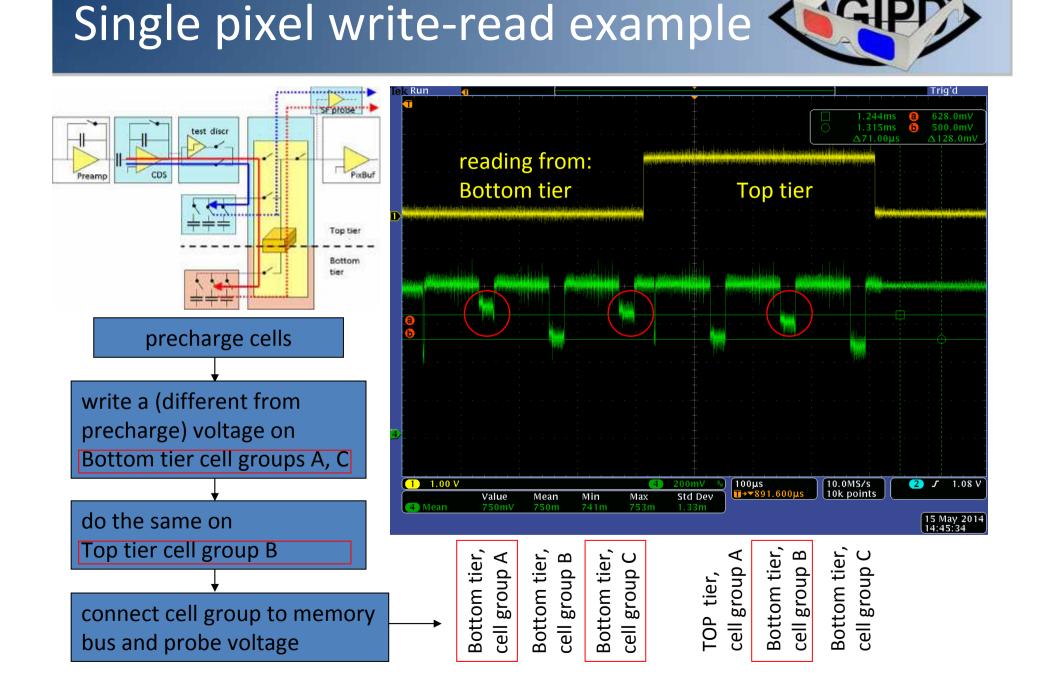

#### Pixel matrix write-read example

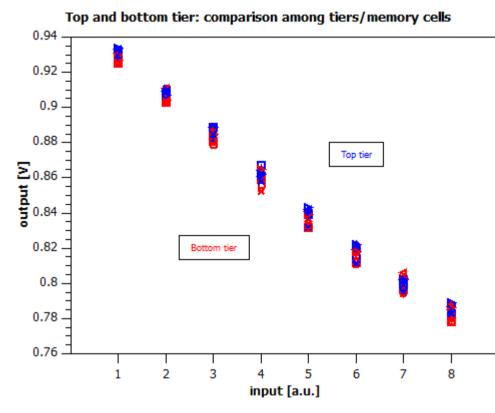

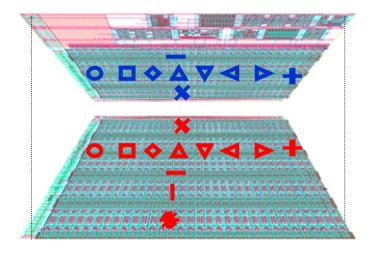

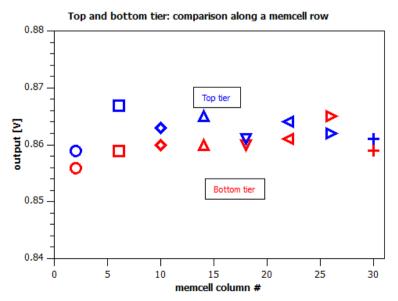

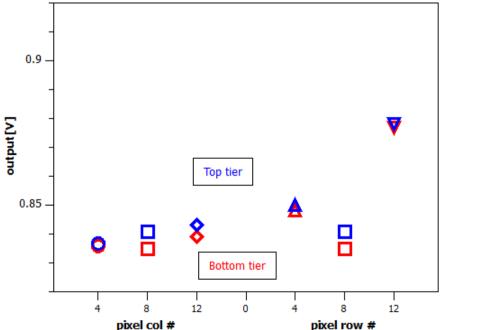

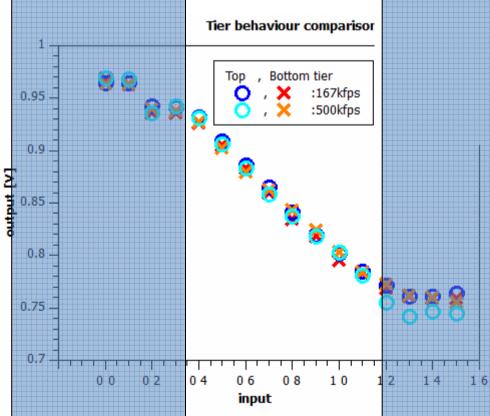

#### Top/Bottom tier: memory cellto-memory cell variations

Comparable (linear) detector response - for charge stored in either in Top/Bottom tier - for different memory cells in the same pixel, independently from their location. Slight pedestal offset, to be investigated further

#### 1 pixel in the array

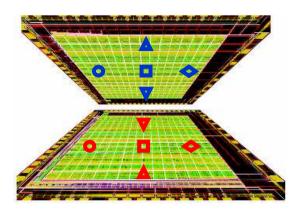

## Top/Bottom tier: pixel-to-pixel & chip-to-chip variations

Different pixels/samples: slightly higher variations. However, outputs from memory cells in the Top/Bottom tier of the same pixel remain similar. Process parameter dispersion in the active pixel circuitry is suspected.

Per-pixel calibration in any case needed.

Top and bottom tier: comparison along a pixel row / column

0.9 Top tier B 0.85 Β Vout [V] Bottom tier 0.8 + 0.75 3 5 9 10 6 7 8 chip #

Top and Bottom tier: comparison among different chips

# Conclusions and future work <

Extending photon science detectors in the third dimension:

the 3D-AGIPD case

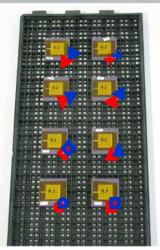

Prototype produced: T13C11 3DIC MPW run (through CMP)

- GF130nm tech, Tezzaron 3D-process, 2 tiers, face-to-face

- 256 pixel array (200um, 544 images memory depth) + test structures

First evaluations

- good TSV, tier-to-tier contact characteristics (10/10)

- 8/10 samples with pixel array working as expected

- able to store/recover info both Top/Bottom tiers

Future work:

- design of improved prototype

- investigation/mitigation of performance dispersion

- investigation of storage cell leakage & rad tolerance of the 3D assembly

#### Backup

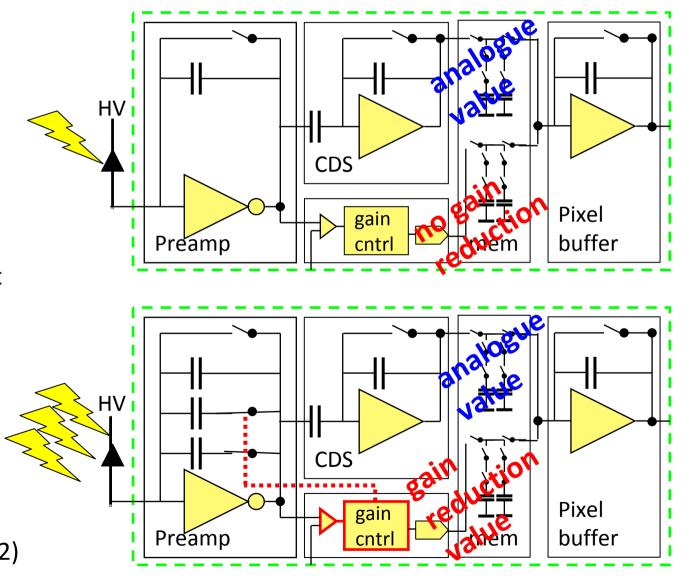

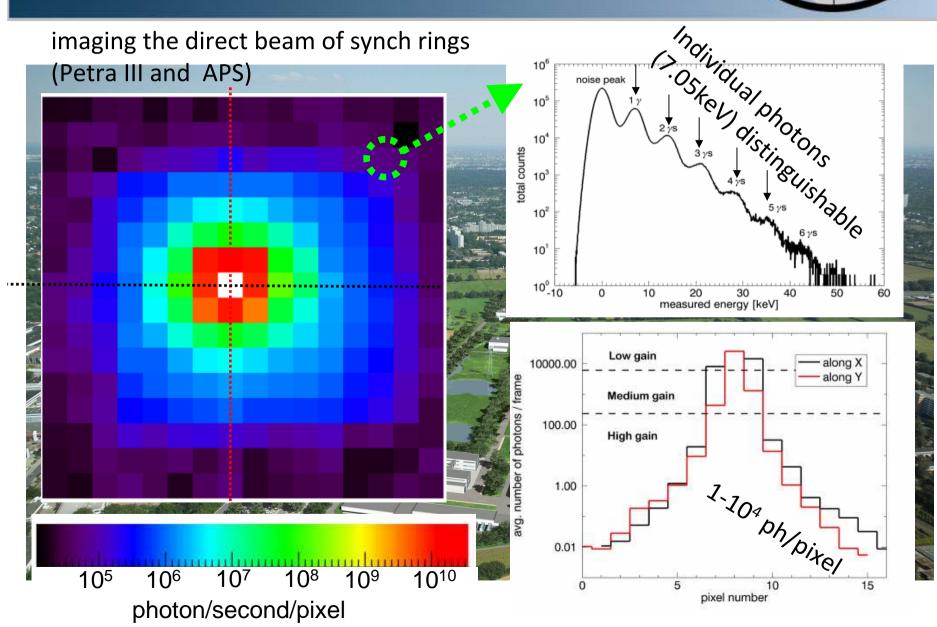

# Adaptive Gain Concept

real-time adjustment of the feedback capacitance depending on the photon flux

60fF/3fF/10fF dyn. switching => adaptable gain O(2)

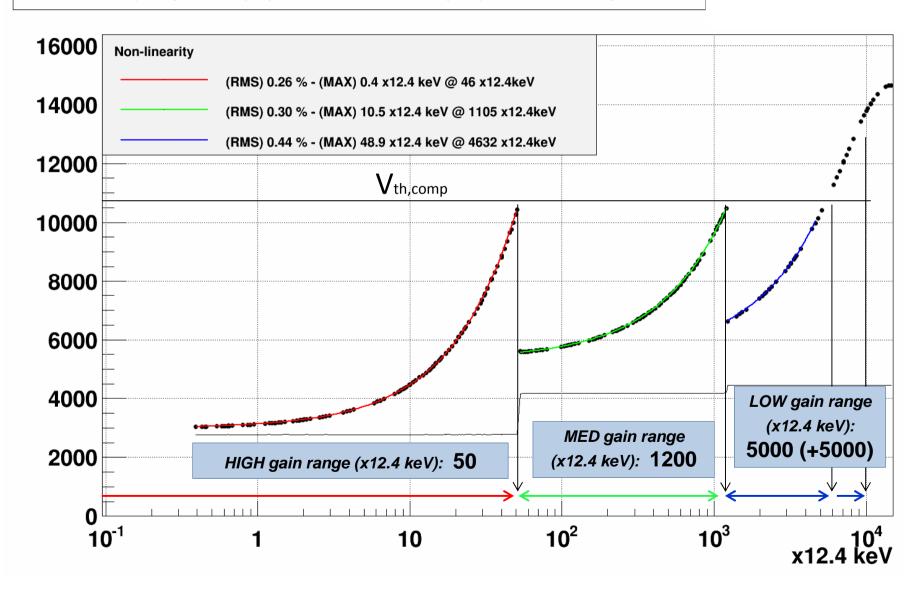

# Multi-Gain Dynamic Range

AGIPD1.0 - Chip 1 - Dynamic Range by LASER (IR) - (Internal Biasing, Chip clock: 40 MHz, CDS gain LOW)

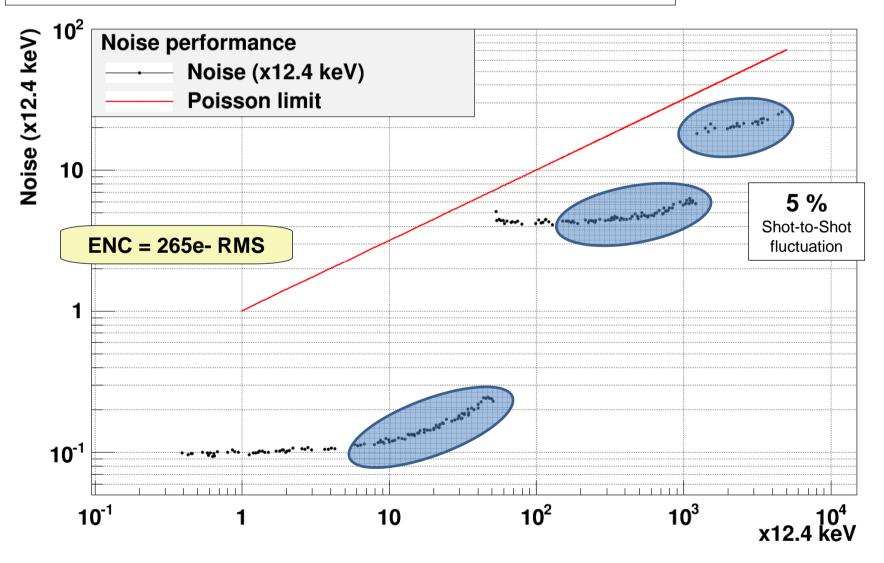

# Noise

AGIPD1.0 - Chip 1 - Noise over Dynamic Range (x12.4 keV) - LASER (IR)

# A.G.I.P.D. (2D)

10<sup>3</sup>

10<sup>4</sup>

10<sup>2</sup>

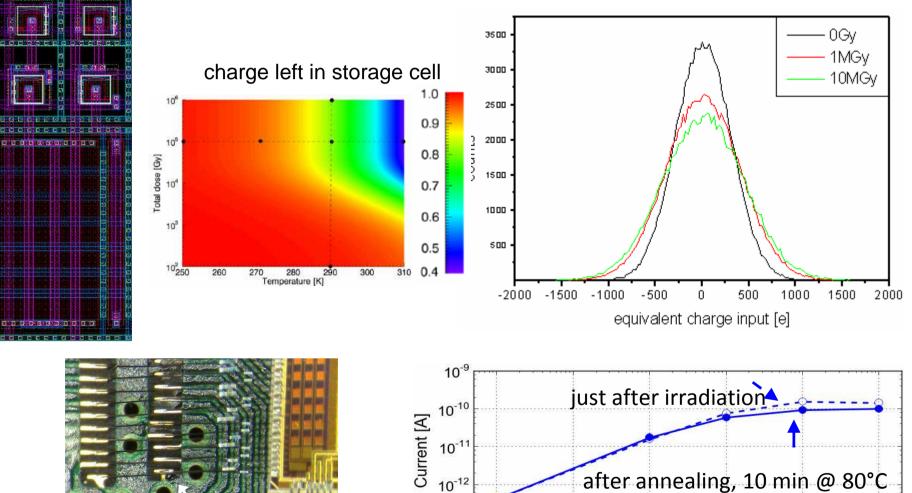

#### Irradiating AGIPD

10-12

10<sup>-13</sup>

10<sup>-1</sup>

10<sup>0</sup>

10<sup>1</sup>

Dose [kGy]

# Test summary

| chip # | daisy chains<br>(TSV & tier-to-tier) | 2D test circuits | single pixel<br>test struct | 16x16 matrix<br>(CDS stage<br>input) | power<br>consumption |

|--------|--------------------------------------|------------------|-----------------------------|--------------------------------------|----------------------|

|        | Top&Bottom tier                      | Top tier         | Top&Bottom<br>tier          | Top&Bottom<br>tier                   |                      |

| 1      | unbroken                             | not responding   | not responding              | not responding                       | 3.75 mW              |

| 2      | unbroken                             | responding       | not responding              | not responding                       | 24.75 mW             |

| 3      | unbroken                             | not responding   | responding                  | responding                           | 31.05 mW             |

| 4      | unbroken                             | responding       | responding                  | responding                           | 24.3 mW              |

| 5      | unbroken                             | responding       | responding                  | responding                           | 26.25 mW             |

| 6      | unbroken                             | responding       | responding                  | responding                           | 30.15 mW             |

| 7      | unbroken                             | responding       | responding                  | responding                           | 30.9 mW              |

| 8      | unbroken                             | responding       | responding                  | responding                           | 31.2 mW              |

| 9      | unbroken                             | responding       | responding                  | responding                           | 26.7 mW              |

| 10     | unbroken                             | responding       | responding                  | responding                           | 30.0 mW              |

as expected unexpected

### Behaviour comparison of Top/Bottom tier storage cells

tested up to 500kfps (limit of current test setup, to be improved for 4.5Mfps test)

expected operation region of the circuit: comparable (linear) behaviour of the detector output, whether the charge is stored in/read from storage cells located on the Top tier or Bottom tier

## memcell comparison

3DAGIPD0

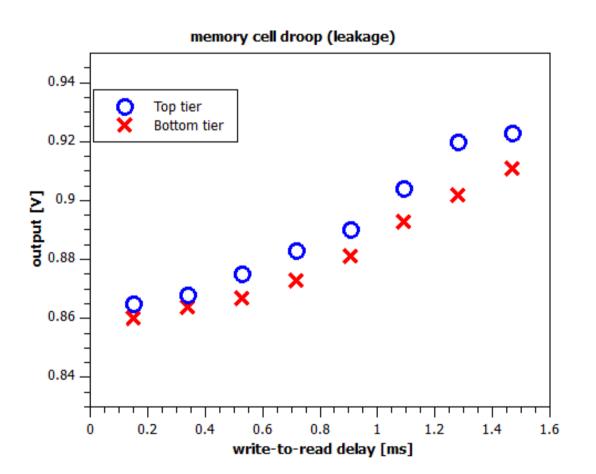

## Open issue: charge leakage

significant parasitic leakage of charge stored in memory cells

Memory cell layout to be optimized Temperature dependence to be investigated