# Towards AGIPD1.0

# Changes arising from the characterization of AGIPD prototype chips

Roberto Dinapoli, <u>Dominic Greiffenberg</u>, Aldo Mozzanica, Bernd Schmitt, Xintian Shi Paul Scherrer Institut (PSI) – SLS Detector Group

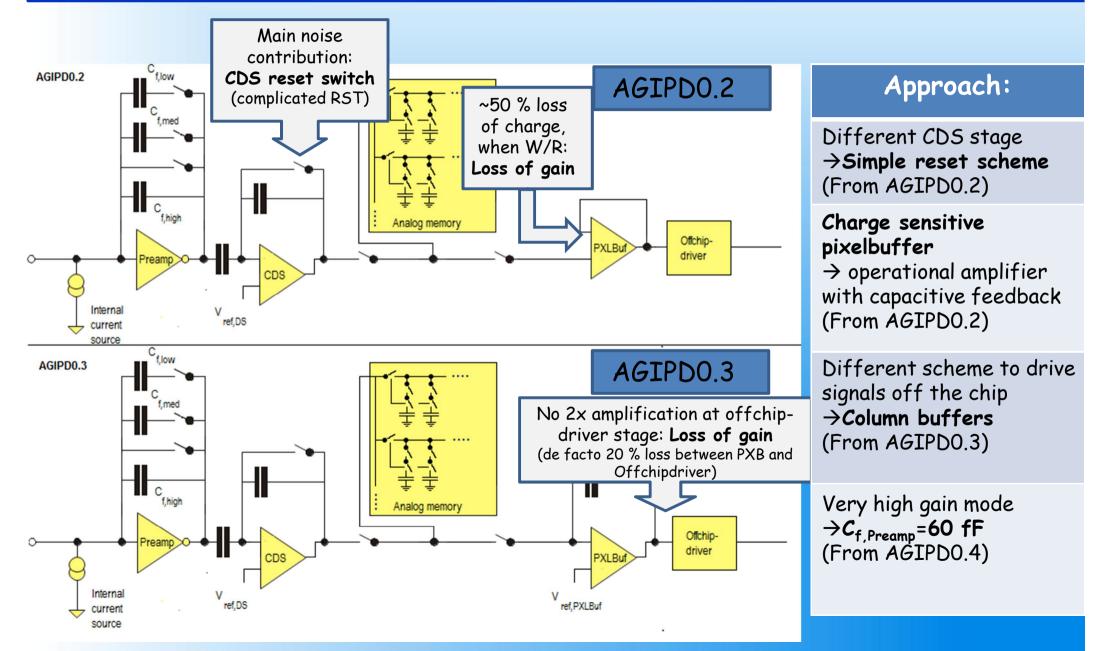

## The AGIPD prototype chips

|                                                                    | AGIPD<br>0.2                                                                                                                                                                                                                                                                                                                                                                          | AGIPD<br>0.3                                                                                                                                                              | AGIPD<br>0.4                                                                                                                                                                                                                           |

|--------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Properties                                                         | - Pixel matrix: 16 x 16 / Pixel size: 200 um x 200 um<br>- Dynamic gain switching with three gain stages:<br>High (C <sub>f,high</sub> = 100 fF / 60 fF for some pixels in AGIPD0.4) -<br>Med (C <sub>f,medium</sub> =3 pF) - Low (C <sub>f,low</sub> = 10 pF)                                                                                                                        |                                                                                                                                                                           |                                                                                                                                                                                                                                        |

| Preamplifier                                                       | <ul> <li>-'Standard preamp<sup>1</sup>'         <ul> <li>-'Fast preamp<sup>2</sup>'</li> <li>-'Standard preamp' with protection diode between the input and VDD</li> </ul> </li> <li><sup>1</sup>CMOS inverter with a DC gain of ~20</li> <li><sup>2</sup> As 'standard', but twice the channel width with respect to standard preamplifier → faster, drags higher current</li> </ul> | - ' <b>Standard</b> preamp'<br>- ' <b>Fast</b> preamp'                                                                                                                    | -'Standard preamp'<br>with either 60 fF or 100<br>fF feedback capacitance<br>- 'Standard preamp' with<br>protection diode<br>between the input and<br>VDD (100 fF)<br>- 'Standard preamp' with<br>a pmos protection switch<br>(100 fF) |

| CDS stage<br>( <u>c</u> orrelated <u>d</u> ouble <u>sa</u> mpling) | <b>Operational amplifier</b><br>with capacitive feed-<br>back, AC coupled to<br>preamp: $C_{coupling}/C_{f,CDS}=2$<br>- Rather complicated reset<br>scheme to remove the<br>offset of the opamp                                                                                                                                                                                       | Operational amplifier<br>with capacitive<br>feedback,<br>two different options of AC<br>coupling to preamp:<br>$C_{coupling}/C_{f,CDS}$ =1 and 2<br>- Simple reset switch | Operational amplifier<br>With capacitive feed-<br>back, two different options of<br>AC coupling to preamp:<br>$C_{coupling}/C_{f,CDS}$ =1 and 2<br>- Simple reset switch                                                               |

## The AGIPD prototype chips

|               | AGIPD<br>0.2                                                                                                                                                                                                                                                 | AGIPD<br>0.3                                                                                                                                   | AGIPD<br>0.4                                                                |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|

| Storage cells | Two different kinds of<br>storage cells:<br>- Switches:<br>Low power pFET<br>Regular VT pFET<br>- Capacitor:<br>Thick gate nFET<br>- 'Active storage cells',<br>buffered in order to keep<br>a zero voltage drop over<br>column switch to reduce<br>leaking  | Two different kinds of<br>Storage cells:<br>- <b>Switches:</b><br>Low power pFET<br>Regular VT pFET<br>- <b>Capacitor:</b><br>Thick gate nFETs | -Switches:<br>Regular VT pFETs<br>-Capacitor:<br>Thick gate nFETs           |

| Pixelbuffer   | Voltage follower,<br>i.e. voltage sensitive<br>- precharging of parasitic<br>capacitance is necessary<br>with either CDS stage or<br>precharge scheme<br>- readout of pixel possible<br>with directly connecting the<br>readout chain to the pixel<br>buffer | Operational amplifier<br>with capacitive<br>feedback,<br>i.e. charge sensitive                                                                 | Operational amplifier<br>with capacitive feedback,<br>i.e. charge sensitive |

#### Status: Noise performance AGIPD0.2 & AGIPD0.3

#### Summary: AGIPD noise contributions

| Component                                                                             | AGIPD0.2<br>(std preamp) <sup>a</sup>                 | AGIPD0.2<br>(std preamp) <sup>b</sup>                  | AGIPD0.3                                        | AGIPD0.4<br>(C <sub>f,high</sub> =100 fF)         | AGIPDO.4<br>(C <sub>f,high</sub> =60 fF)          |

|---------------------------------------------------------------------------------------|-------------------------------------------------------|--------------------------------------------------------|-------------------------------------------------|---------------------------------------------------|---------------------------------------------------|

|                                                                                       | <b>10 SCR,</b><br>200 ns, V <sub>ref,DS</sub> = 0.6 V | $\frac{1 \text{ SC W/R}}{2 \mu s, V_{ref,DS} = 0.6 V}$ | 1 SC W/R,<br>200 ns, V <sub>ref,DS</sub> = 0.5V | 1 SC W/R,<br>200 ns, V <sub>ref,DS</sub> = 0.65 V | 1 SC W/R,<br>200 ns, V <sub>ref,DS</sub> = 0.65 V |

| Preamp<br>(Reset switch)                                                              | 153 ± 1<br>(317 ± 2)                                  | <b>212</b> ± 3                                         | <b>115</b> ± 3                                  | <b>210</b> ± 3                                    | 150 ± 3                                           |

| CDS<br>(Reset switch)                                                                 | 251 ± 2<br>(236 ± 2)                                  | <b>258</b> ± 3                                         | <b>239</b> ± 5                                  | <b>221</b> ± 2                                    | 133 ± 2                                           |

| Readout<br>chain<br>(PXLBuffer <sup>2</sup> +Offchip <sup>2</sup> )<br>(Reset switch) | <b>273</b> ± 2                                        | 561 ± 7                                                | <b>438</b> ± 7°<br>(197 ± 4)                    | <b>311</b> ± 1 (191 ± 1)                          | 225 ± 3<br>(144 ± 1)                              |

| (oversampled)                                                                         | <b>401</b> ± 2 (281 ± 2)                              | 654 ± 8<br>(413 ± 5)                                   | 512 ± 10<br>(383 ± 8)                           | <b>436</b> ± 1<br>(394 ± 1)                       | 301 ± 4<br>(270 ± 3)                              |

| <i>Gain</i><br>(ADC/keV)                                                              | 16.38 ± 0.10                                          | 8.34 ± 0.10                                            | 6.09 ± 0.12                                     | 11.18 ± 0.02                                      | 15.99 ± 0.20                                      |

<sup>a,b</sup>Overall noise of standard preamp + protection diode (oversampled): 10 SCR:  $438 \pm 8$  ( $325 \pm 5$ ) | 1 SCWR:  $661 \pm 8$  ( $422 \pm 5$ ) <sup>c</sup>Noise contributions AGIPD0.3 readout chain: Pixelbuffer=  $332 \pm 7$  | Offchip=  $285 \pm 6$

## 'Presummary': AGIPD0.4 status

| Component            | Status                                                                                     | Result                                                                  |

|----------------------|--------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|

| Noise                | <ul> <li>C<sub>f</sub>= 60 fF</li> <li>CDS gain HIGH (x2)</li> <li>Offchip x1.5</li> </ul> | $\frac{\text{Noise (ENC):}}{(301 \pm 4) e} $ (270 ± 3) e- (oversampled) |

| Protection measures  | <ul><li>Diodes</li><li>Nmos switches</li></ul>                                             | <b>Basically decided</b>                                                |

| Speed (Write to SC)  | • (Up to now) Just<br>measured @ 10 MHz<br>not speed optimised                             | Some changes                                                            |

| Speed (Read from SC) | <ul> <li>(Up to now) Not worried<br/>at all about readout speed</li> </ul>                 | Should be fine                                                          |

| Dynamic range        | • With CDS gain HIGH and 60 fF:<br>Good linearity up to feature<br>1000x12.4keV            | , but we'll make<br>it good!                                            |

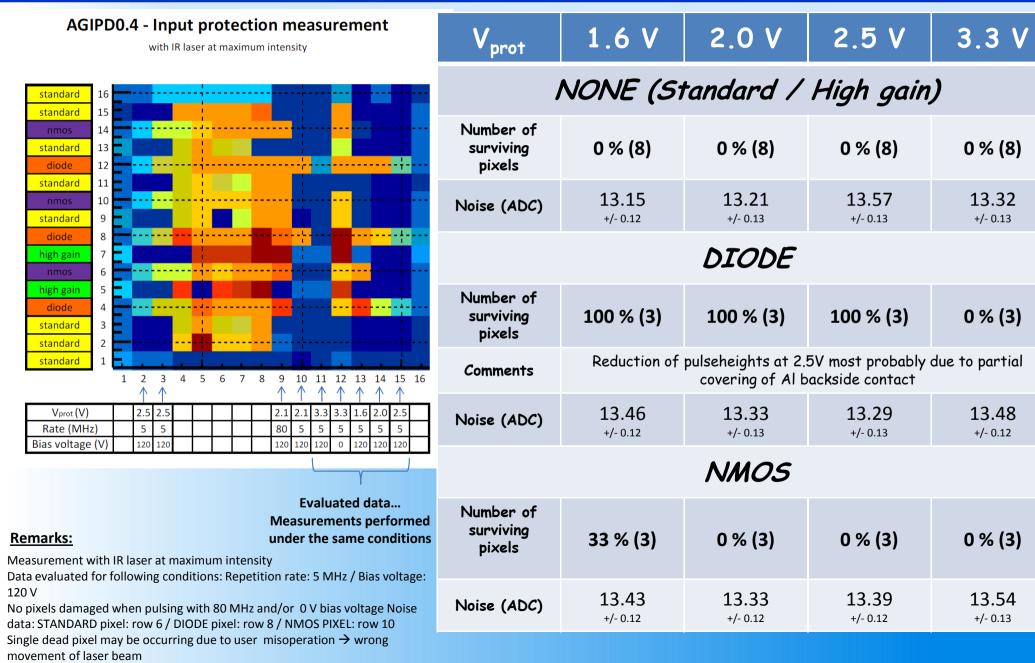

#### Protection measures

• Pixel destruction <u>possible</u> with IR laser (1030 nm) at full power and 5 MHz repetition frequency.

- Probably conducting channel in sensor (due to interaction depth of IR throughout sensor)

- →With bias voltage of 120 V: Pixels die

→ No bias voltage, no dying pixels

• Opens possibility to examine the protection measures...

→Worst case scenario: 120 V swing within few ns

→Investigating the ability to destroy pixels for different voltages at protection circuits (Diode, nmos switch) (Reference is always the standard pixel)

#### Protection measures

#### Protection measures

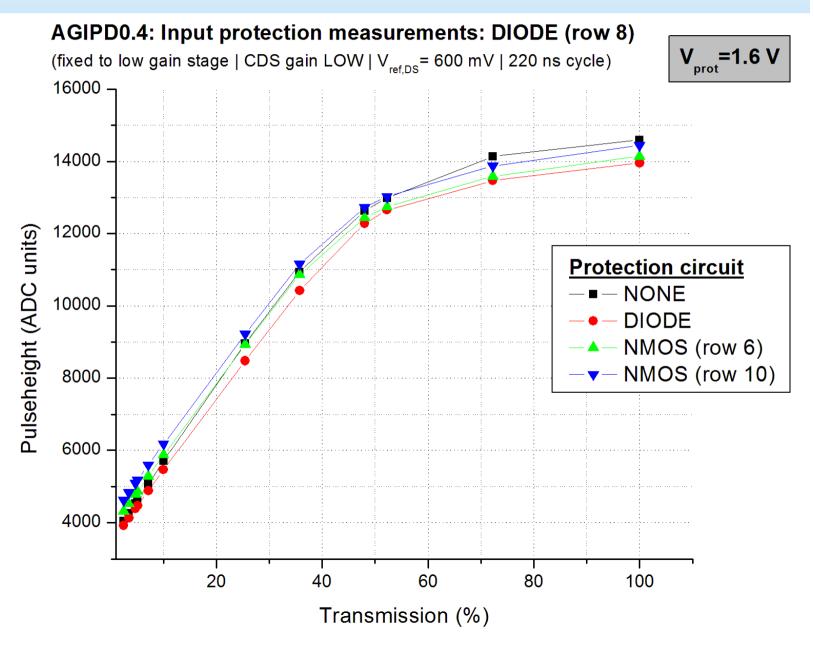

Leaking through protection curcuit?

→ 1.6 V worst case scenario

→Looking at bending of curves for high pulses

→Nmos curves bend clearly for transmission >50 %

→Diode like Standard, yet radiation hardness to be tested

```

// Integration, Write & Reset cycle //

220 ns write-switch-reset cycle @ 80 MHz

SB(en tst curr);

REPEAT(1):

\rightarrow 17 clks = 212.5 ns

for(memclk=0;memclk<1;memclk++) {</pre>

SB(rst preamp);

Investigated 150 ns cycle

SB(set g1 ext);

SB(set g2 ext);

SB(ds sw1);

\rightarrowOnly 12 clks

SB(memcol clk); SB(clk dac);

(Reducing RST time by 2, Reducing Integration time by 3)

REPEAT(1)

CB(memoti clk);CB(clk dac);

REPEAT

SB(en_dmem);SB(en_dmem);

REPEAT(1)

CB(en extgain);

CB(set gl ext);

CB(set g2 ext);

REPEAT(3)

CB(rst preamp);

REPEA<sup>T</sup>

CB(ds

REPEAT

CB(en amem);CB(en dmem);

REPEAT(1);

CB(en tst curr);

REPEAT(1);

```

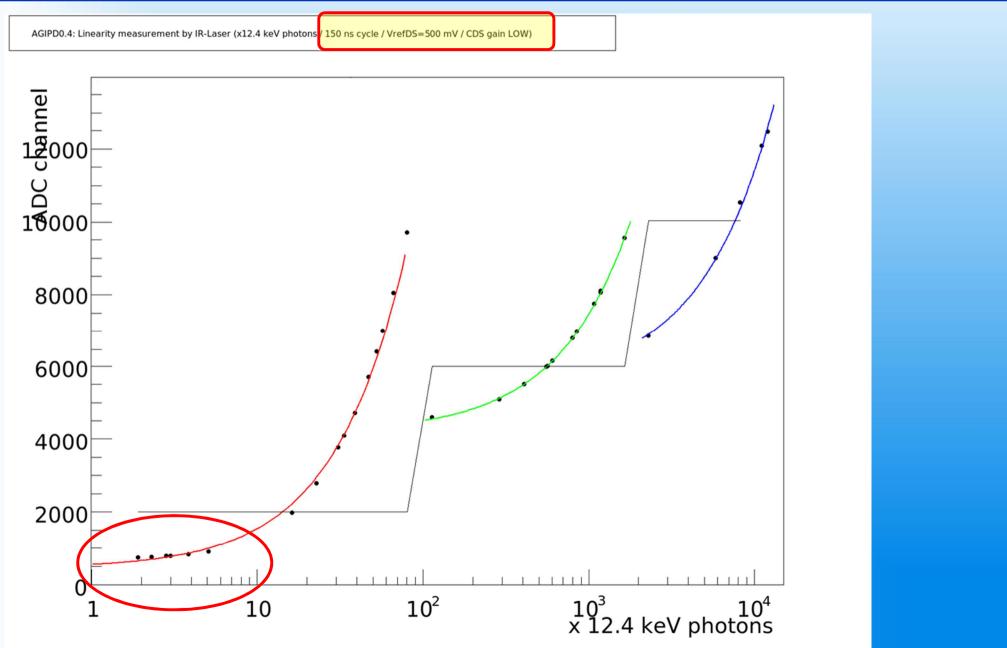

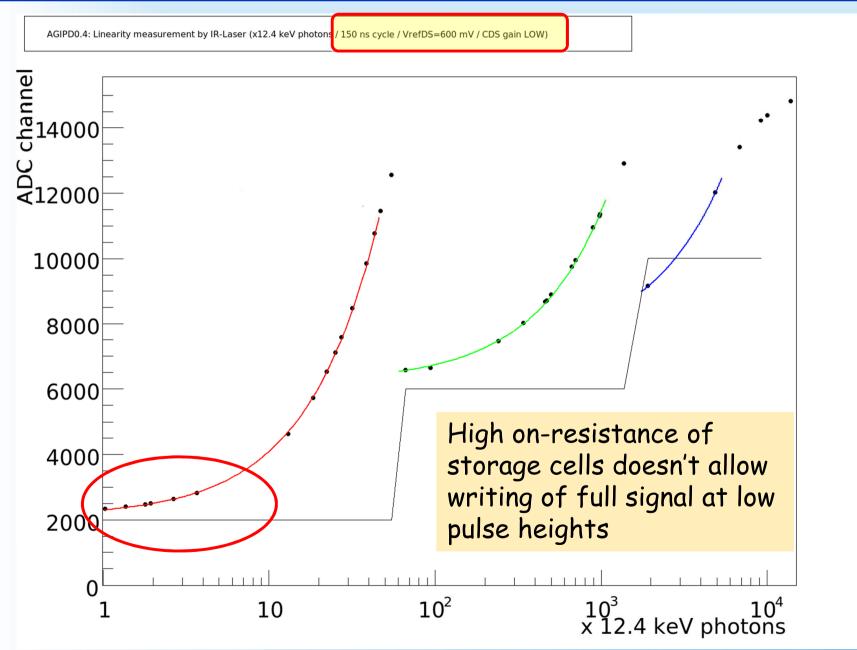

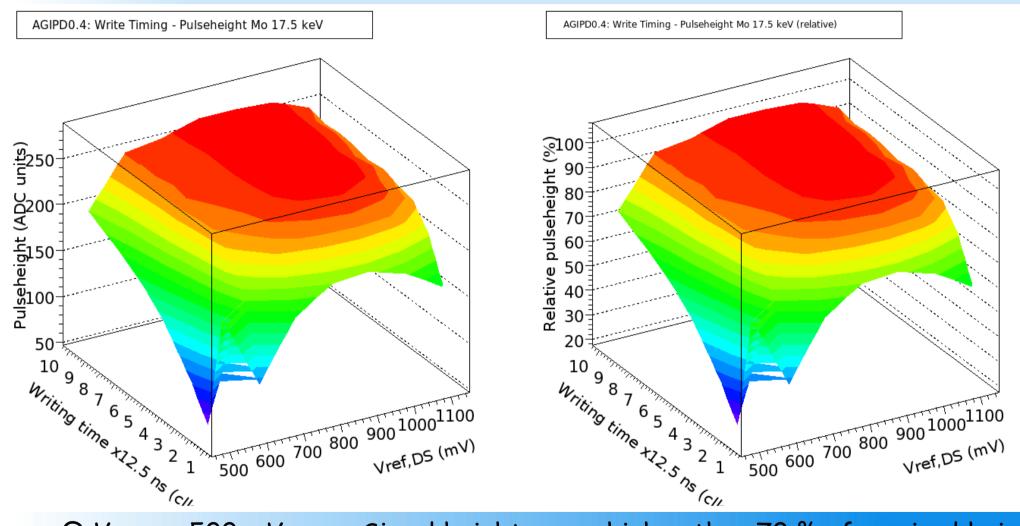

• @ V<sub>ref,DS</sub>= 500 mV: Signal height never higher than 70 % of maximal height due to incomplete writing on storage cell

→ Choosing V<sub>ref,DS</sub>= 600 mV: Losing "only" 10 - 15 %

→ New CDS STAGE: faster, linear up to 1300 mV

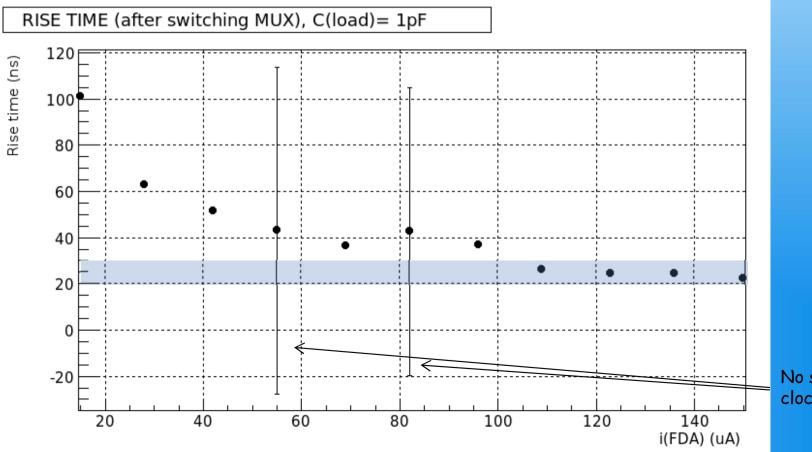

## Speed (Reading)

#### New Chipoutputbuffer:

- Fully differential

- Can drive up to 100  $\Omega$

- Can drive that in 30 ns ...that needed to be verified!

No sync between ADC clock and pattern clock

#### Dynamic Range

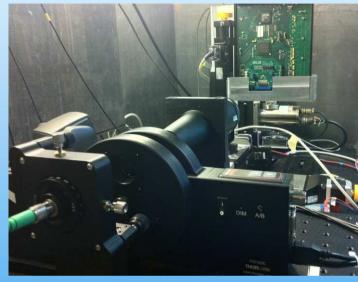

#### Laser Setup:

- Red (660 nm) and IR (1030 nm) laser diodes

- Repetition rate: 5 ... 80 MHz (divider up to 16)

- Power: <11.5 mW (red) / <15 mW (IR)

- 2x Filter wheel  $\rightarrow$  36 combinations

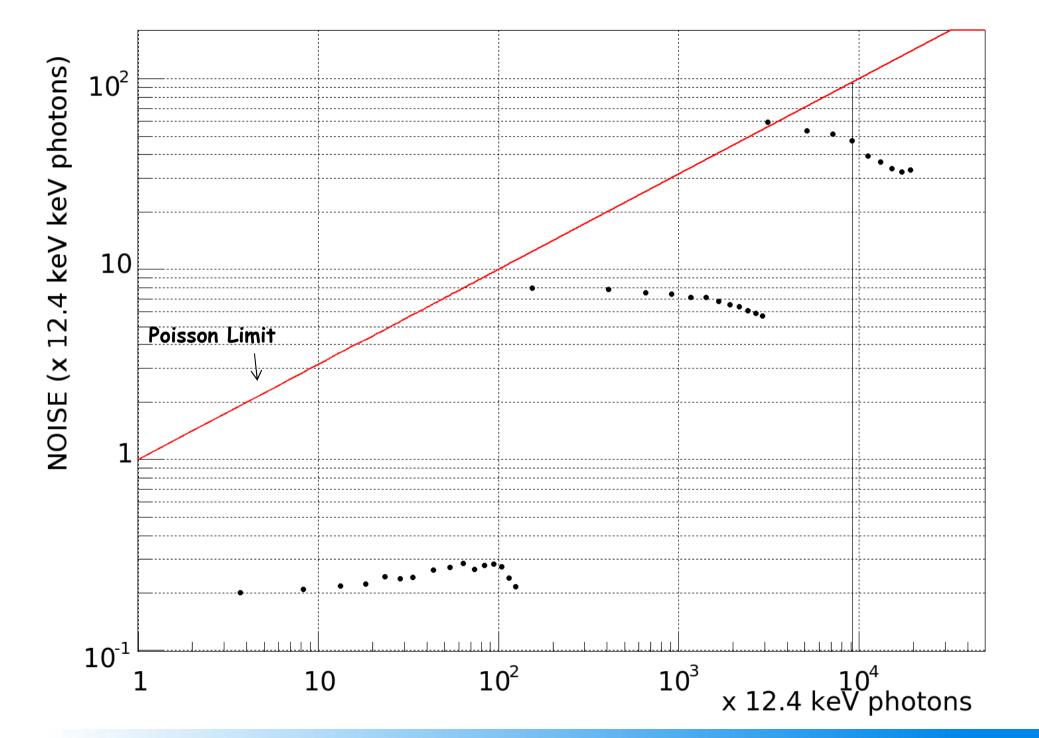

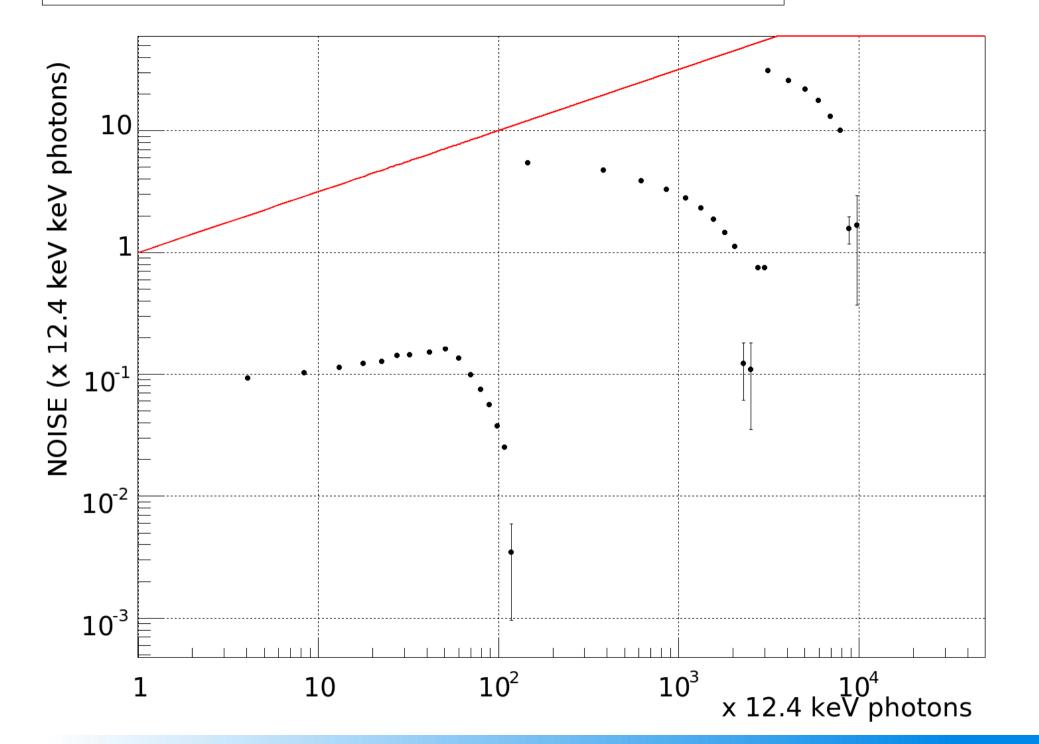

#### BUT shot-to-shot fluctuations, difficult to measure noise

Lamp Setup:

almost perfect constant current source

- simple,

- reliable,

cross calibration possible by energy calibration

## <u>p:</u>

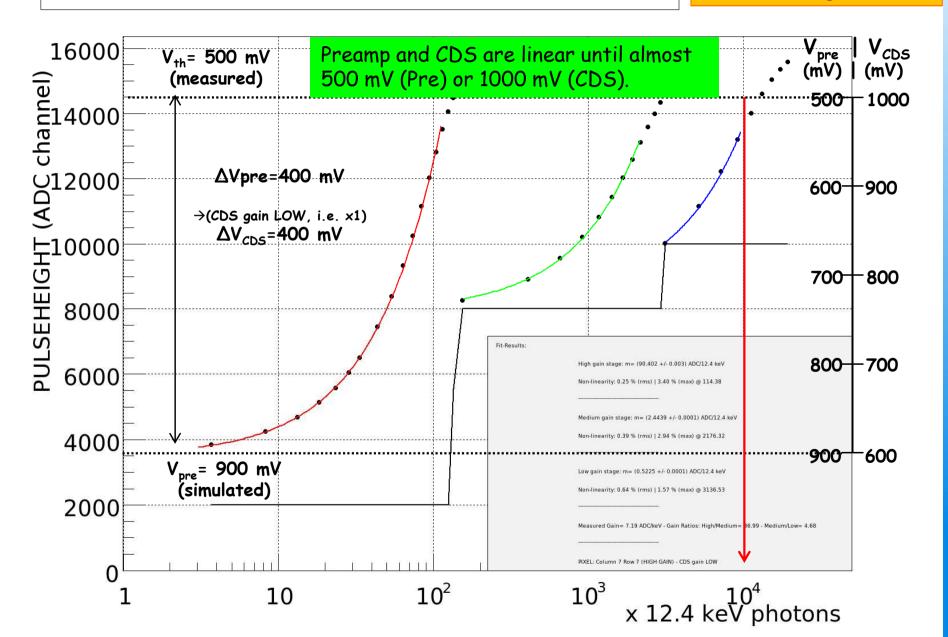

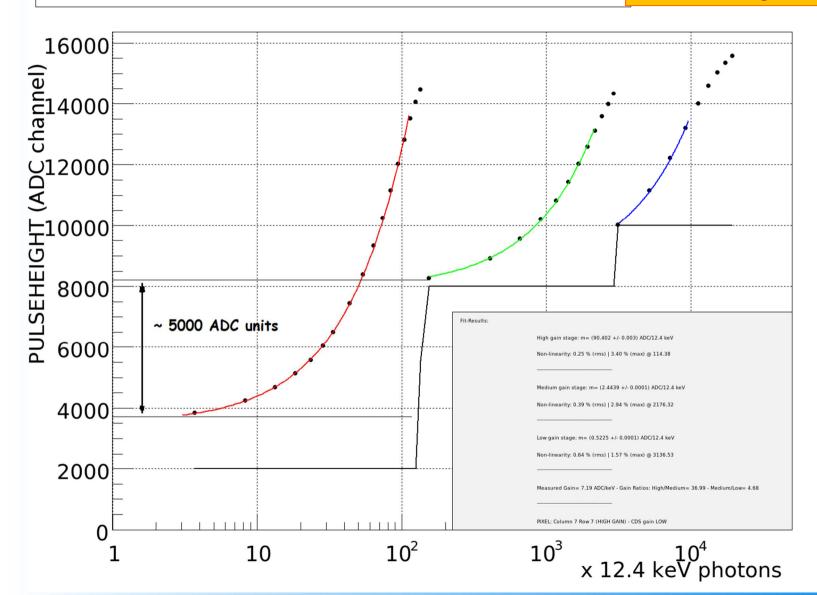

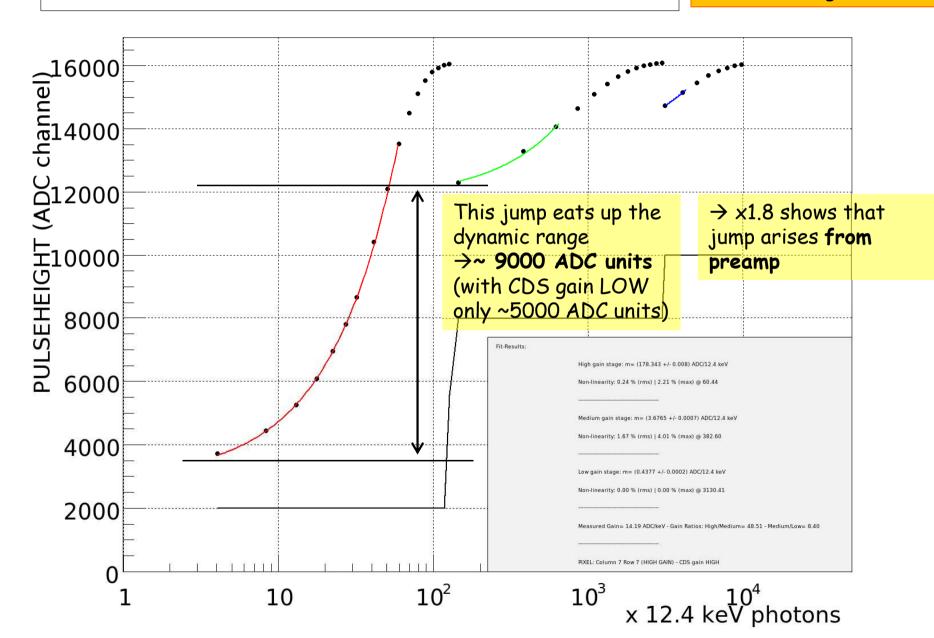

AGIPD0.4: Linearity measurement by Flashlight (x 12.4 keV photons) - Pixel: Column 7 Row 7 (High Gain) - Classical RST (220 ns cycle / VrefDS=600 mV / CDS gain LOW / Cfhigh=60 fF)

60 fF / CDS gain LOW

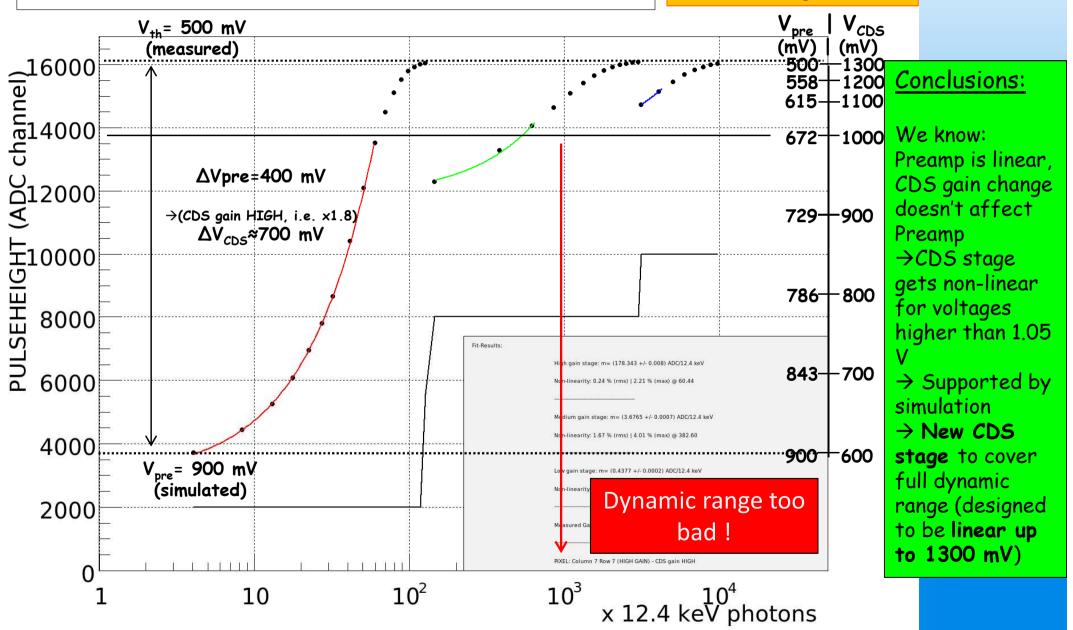

AGIPD0.4: Linearity measurement by Flashlight (x 12.4 keV photons) - Pixel: Column 7 Row 7 (High Gain) - Classical RST (220 ns cycle / VrefDS=600 mV / CDS gain HIGH / Cfhigh=60 fF)

#### 60 fF / CDS gain HIGH

AGIPD0.4: Linearity measurement by Flashlight (x 12.4 keV photons) - Pixel: Column 7 Row 7 (High Gain) - Classical RST (220 ns cycle / VrefDS=600 mV / CDS gain HIGH / Cfhigh=60 fF]

#### 60 fF / CDS gain HIGH

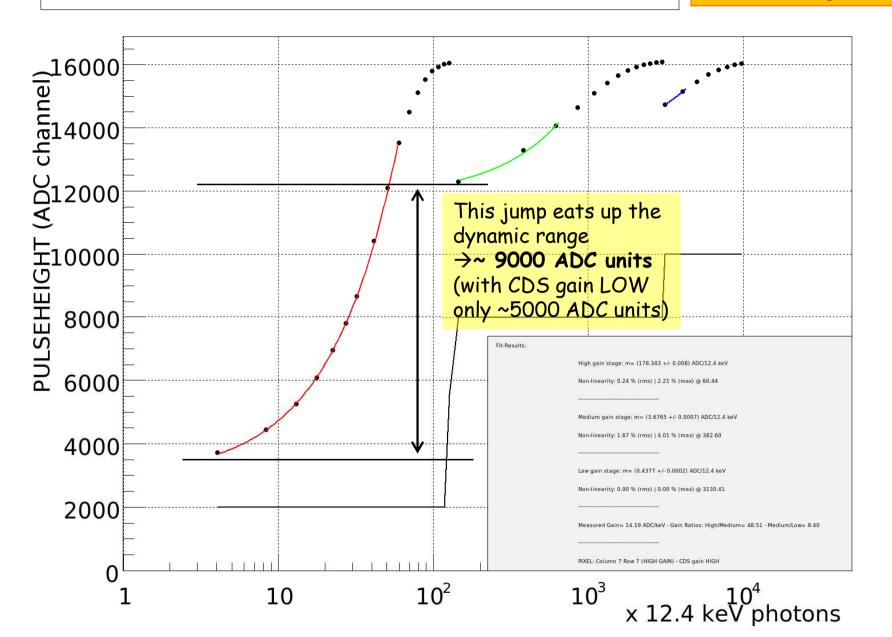

AGIPD0.4: Linearity measurement by Flashlight (x 12.4 keV photons) - Pixel: Column 7 Row 7 (High Gain) - Classical RST (220 ns cycle / VrefDS=600 mV / CDS gain LOW / Cfhigh=60 fF)

#### 60 fF / CDS gain LOW

AGIPD0.4: Linearity measurement by Flashlight (x 12.4 keV photons) - Pixel: Column 7 Row 7 (High Gain) - Classical RST (220 ns cycle / VrefDS=600 mV / CDS gain HIGH / Cfhigh=60 fF)

#### 60 fF / CDS gain HIGH

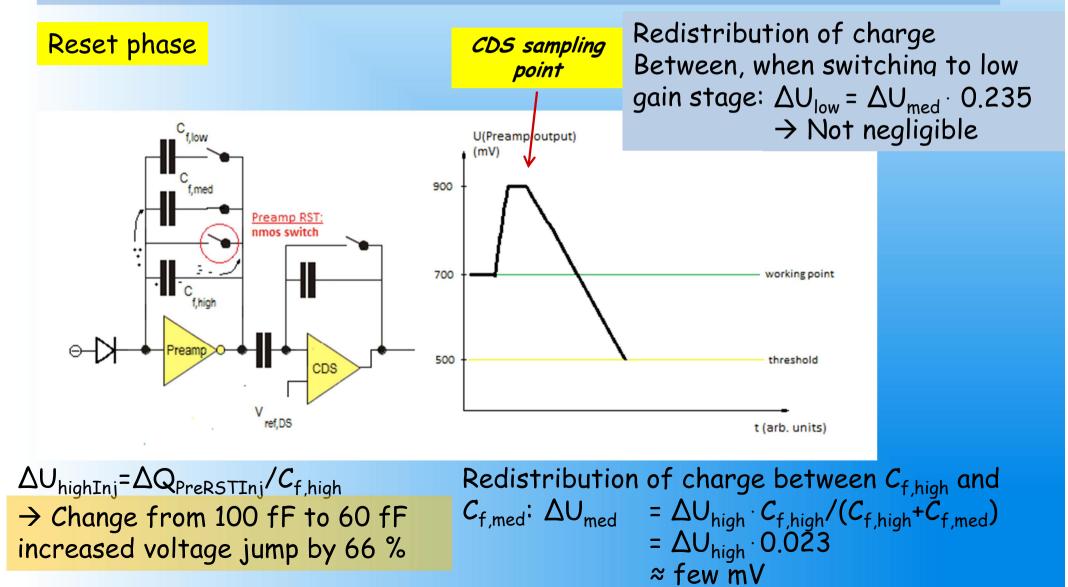

#### Dynamic Range

Jump is due to an actually wanted charge injection in the  $C_{f,high}$  in order to increase the dynamic range of the high gain stage

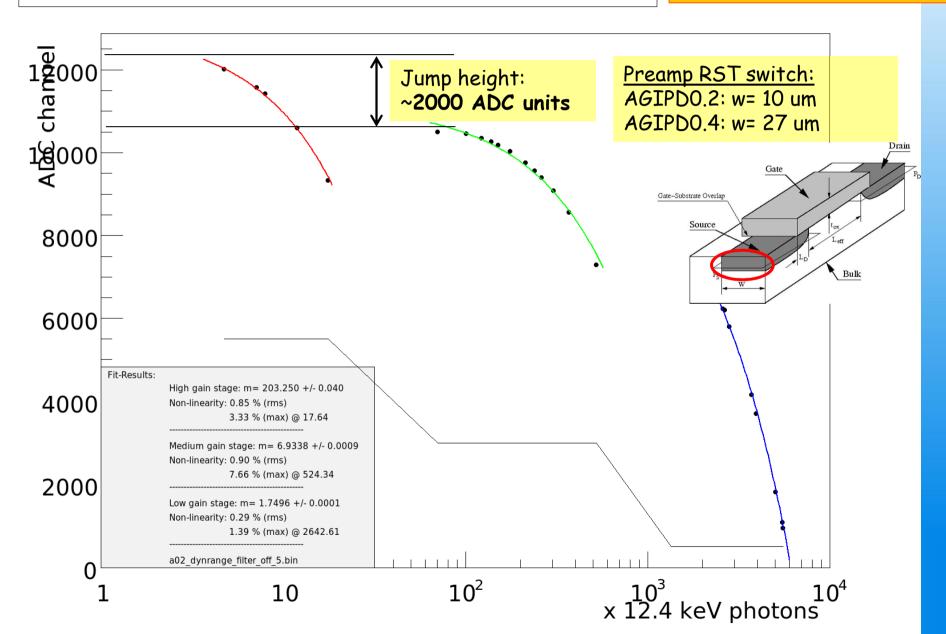

AGIPD0.2: Linearity measurement by IR-Laser (x12.4 keV photons)

#### AGIPDO.2: 100 fF / CDS gain HIGH

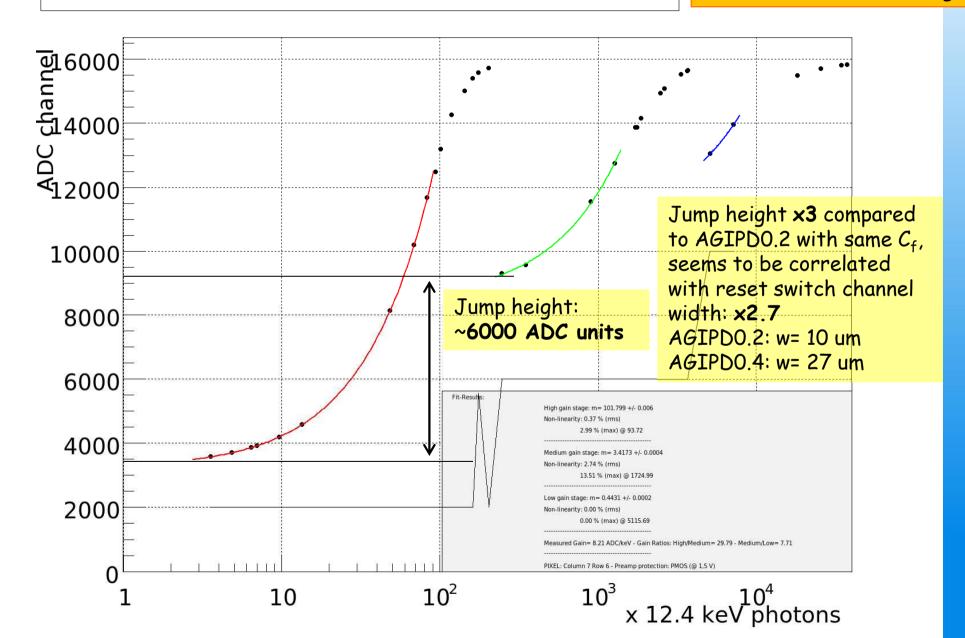

AGIPD0.4: Linearity measurement by IR-Laser (x 12.4 keV photons) - Pixel: Column 7 Row 6 (Preamp protection: PMOS (@ 1,5 V) / 220 ns cycle / VrefDS=600 mV / CDS gain HIGH / Cfhigh=100 fF)

#### AGIPDO.4: 100 fF / CDS gain HIGH

#### Dynamic Range

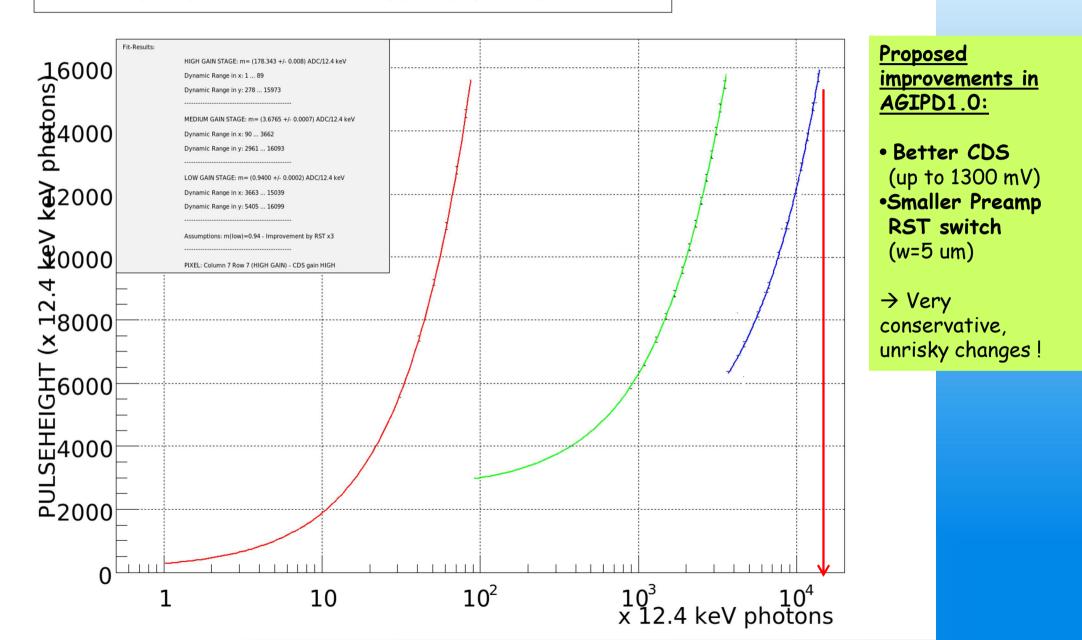

AGIPD1.0: Expected Dynamic Range with Smaller Preamp RST & Improved CDS stage (up to 1.3 V) (CDS gain HIGH / Cfhigh=60 fF)

## 'Real' summary

| Component            | Updated status                                                        | Result                                                                             |

|----------------------|-----------------------------------------------------------------------|------------------------------------------------------------------------------------|

| Noise                | • C <sub>f</sub> = 60 fF<br>• CDS gain HIGH (x2)<br>• Offchip x1.5    | $\frac{\text{Noise (ENC):}}{(301 \pm 4) e}$ (270 ± 3) e- (Sversampled)             |

| Protection measures  | •Diodes<br>• <del>Nmos switches</del>                                 | Radiation hardnækæð/be<br>tested $\rightarrow critical test positive)$             |

| Speed (Write to SC)  | Writing within >150 ns<br>successful                                  | V <sub>ref,DS</sub> needs to be<br>increased to 600 mVy ↓<br>→ Improving CDS stage |

| Speed (Read from SC) | Reading time after<br>switching MUX ~30 ns<br>→ 30 MHz                | Okay I                                                                             |

| Dynamic range        | Should be possible to get to > 1 · 10 <sup>4</sup> × 12.4 keV photons | → Improved CDS stace<br>Nogaloroe229 Vswitch                                       |

# You made it... O You made it... O Thanks for your attention